УДК 004.272:004.383

# И. А. ЖУКОВ, Н. А. КОВАЛЕВ

# Национальный авиационный университет, Украина

# БЫСТРОДЕЙСТВИЕ ЦИФРОВЫХ ИНТЕГРИРУЮЩИХ СТРУКТУР

Предложены алгоритмы функционирования цифровых интегрирующих структур (ЦИС), использующих разработанный метод неавтономного вычисления приращения интеграла Стилтьеса, и способы их построения. Проведены экспериментальные исследования быстродействия при реализации их на базе FPGA. Метод позволяет обеспечить значительное преимущество в быстродействии над квазипараллельными ЦИС, построенными с использованием известного структурного метода, и ЦИС, вычисляющими по правилам параллельной многоразрядной арифметики. Результаты практических исследований подтверждают теоретические оценки и эффективность разработанного метода для значительного ускорения интегральных вычислений в ЦИС.

**Ключевые слова:** цифровые интегрирующие структуры, неавтономная арифметика (Online Arithmetic), избыточные системы счисления, быстродействие, аппаратурная сложность, FPGA.

### Введение

В настоящее время объектом исследований и разработок вновь становятся однородные вычислительные среды (ОВС) [1]. В этой связи на новом уровне рассматривают цифровые интегрирующие структуры (ЦИС) [2], - однородные специализированные ОВС, состоящие из цифровых интеграторов (ЦИ). Выполняя численное интегрирование по Стилтьесу систем уравнений Шеннона, ЦИС могут эффективно решать широкий класс задач, находящихся в пространстве непрерывных функций, в реальном времени при моделировании сложных систем и управлении высокоскоростными объектами. Они обладают также повышенными характеристиками надежности и живучести. Оптимальными по быстродействию, точности и аппаратурной сложности являются параллельные ЦИС, рассчитанные на работу с фиксированной запятой. Современные развитые элементные базисы (FPGA, CPLD, ASIC) позволяют раскрыть потенциал ЦИС в их интегральных исполнениях.

В [3] показана эффективность применения средств неавтономной арифметики (Online Arithmetic) при аппаратной реализации ЦИС: значительное совмещение вычислений на шаге интегрирования; сокращение объема оборудования для хранения промежуточных результатов интегрирования; многократном уменьшении сложности коммутационной сети (КМС).

Предложенная структура квазипараллельной ЦИС [4], реализующей интегральные вычисления в неавтономном режиме, содержит определенное число одинаковых «слоев», каждый из которых является параллельной ЦИС. Однако выходы ЦИ каждого «слоя» посредством собственной КМС соединяются не между собой, а с ЦИ следующих «слоев». В такой тороидальной структуре может

достигаться значительное совмещение (конвейеризация) интегральных вычислений на разных шагах. Дальнейшее ускорение достигается уменьшением начальной задержки на формирование старшей цифры интегрального приращения, которая определяет длительность шага интегрирования. В предложенном методе неавтономного вычисления приращения интеграла в соответствии с формулой интегрирования по Стилтьесу в избыточной симметричсчисления основанием c  $k = 2^{\nu} (\nu \in N^*)$  и цифрами  $\{-k/2, k/2\}$ составляет 2-3 такта с момента поступления старших цифр входных интегральных переменных, что значительно сокращает длительность шага и увеличивает степень распараллеливания интегральных вычислений, что может существенно повысить быстродействие ЦИС. Получены теоретические оценки быстродействия рассматриваемых ЦИС, проведено их сравнение с другими структурами.

**Цель статьи** — экспериментальное исследование и сравнение быстродействия ЦИС, применяющей разработанный метод неавтономного вычисления приращения интеграла Стилтьеса, с известными структурами при реализации на базе ПЛИС типа FPGA.

## 1. Модели ЦИС

Скорость интегрирования в ЦИС определяется быстродействием ЦИ. В соответствии с разработанным методом неавтономного вычисления интегрального приращения предложены алгоритмы формирования его цифр с начальной задержкой в 2 такта, которые могут выполняться за такт.

Первый алгоритм определения цифр  $z_i$  интегрального приращения ( $H_i$  и  $R_i$  – вспомогательные переменные) имеет вид:

6.  $R_i = H_i - z_i$ .

Здесь Z соответствует приращению интеграла Стилтьеса, Y — подынтегральной функции,  $X_p$  — ее приращениям,  $X_q$  — приращениям переменных интегрирования на разных его шагах,  $x_i$  и  $y_i$  — их цифрам. Индексы k(s) і l(s) ( $s=\overline{l,m}$ ) определяют порядок задействования приращений в зависимости от порядка точности N формулы интегрирования по Стилтьесу.  $2^{-l}$  і  $2^{-j_s}$  — масштабные коэффициенты. Значения m и констант  $C_s$  также зависят от N. Приращения представлены в избыточной симметричной системе исчисления с основанием  $k=2^v$ ,  $v\in N^*$  и цифрами  $\left\{\overline{-k/2,k/2}\right\}$ , по модулю меньше единицы, имеют разряд левее и n разрядов правее запятой.

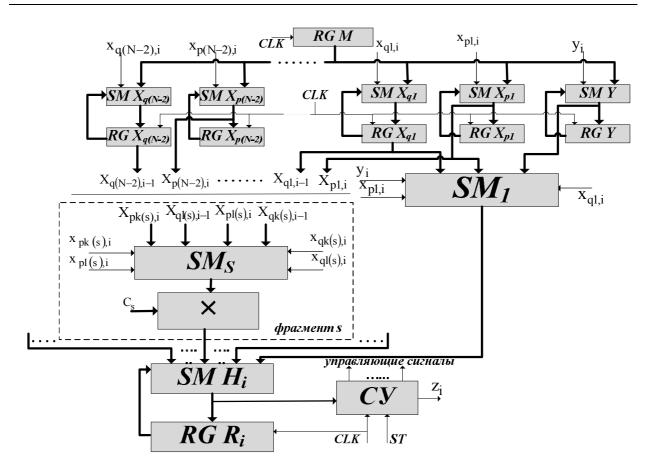

Соответствующая структура квазипараллельного ЦИ (рис. 1) является основой модели ЦИС (обозначим как ЦИС N 1) при реализации в кристаллах FPGA с большим числом встроенных умножителей ( $Embedded\ Multiplier$ ,  $DSP\ blocks$ ) и блоков памяти ( $Memory\ Blocks$ ), которые эффективно реализуют мультипликативные, аддитивные операции и их комбинации с меньшим расходом логических ресурсов микросхемы.

Второй алгоритм использует лишь операции сложения и сдвига. Учитывая, что каждую его итерацию также можно выполнять за такт, быстродействие соответствующего ЦИ и ЦИС (ЦИС № 2) в целом может оказаться относительно высоким даже

при реализации в бюджетных микросхемах FPGA ( $F_{pk}$ ,  $F_{qk}$  – вспомогательные переменные):

1.Для i=0 до (n'+2) выполнить пп. 2-7, приняв для всех переменных соответствующего вида:  $X_{pl,-1}=0; X_{ql,-1}=0$  ;  $F_{p,-1}=0$  и  $F_{q,-1}=0$  ;  $C_{s-1}=C_s$ ;  $R_{-1}=0$  .

2.  $X_{pl,i} = X_{pl,i-l} + x_{pl,i} k^{-i}$ ; для всех переменных соответствующего вида:  $F_{p,i} = F_{p,i-l} + x_{p,i} C_{s,i-l}$ ;  $Y_i = Y_{i-1} + v_i k^{-i}$ .

$$\begin{split} 3. \ \ H_i &= kR_{i-1} + k^{-2} \big[ y_i X_{ql,i-1} + x_{ql,i} Y_i + \\ &+ 2^{-l} \left( x_{pl,i} X_{ql,i-1} + x_{ql,i} X_{pl,i} \right) + \\ &+ \sum_{s=1}^{m} 2^{-j_s} \left\{ \left( x_{ql(s),i} F_{pk(s),i} + x_{pk(s),i} F_{ql(s),i-1} \right) - \\ &- \left( x_{qk(s),i} F_{pl(s),i} + x_{pl(s),i} F_{qk(s),i-1} \right) \right\} \big]. \end{split}$$

4.  $X_{ql,i}=X_{ql,i-1}+x_{ql,i}k^{-i}$ ; для всех переменных вида  $F_{q,i}=F_{q,i-1}+x_{q,i}C_{s,i-1}$  .

$$5. \ C_{s,i} = C_{s,i-l} k^{-l} \left(s = \overline{l,m}\right).$$

$$\begin{cases} -k/2, \ \text{если Hi} < \left(l-k\right)/2 \\ \dots \\ -1, \ \text{если} -3/2 \le \text{Hi} < -1/2; \\ 0, \ \text{если} -1/2 \le \text{Hi} < 1/2; \\ 1, \ \text{если} \ 1/2 \le \text{Hi} < 3/2; \\ \dots \\ k/2, \ \text{если Hi} \ge \left(k-1\right)/2. \end{cases}$$

7.

$$R_i = H_i - z_i$$

.

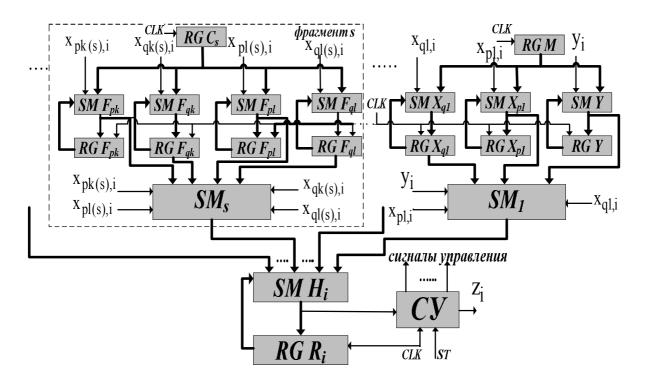

На рис. 2 представлена соответствующая этому алгоритму структура квазипараллельного ЦИ. Для сравнения рассмотрим также:

модель квазипараллельной ЦИС (ЦИС № 3), основу которой составляют ЦИ, разработанные в соответствии с известным структурным методом построения квазипараллельных вычислительных устройств [3]. Он предполагает коммутацию операционных блоков (ОБ) умножения и сложения в соответствии с ярусно-параллельной формой (ЯПФ) графа вычисления приращения интеграла Стилтьеса. Существенная величина начальной задержки формирования старшей цифры интегрального приращения определяется большим числом квазипараллельных ОБ, входящих в критический путь ЯПФ. Она может привести к большей длительности шага и меньшему быстродействию этой модели ЦИС;

– модель ЦИС (ЦИС № 4), функционирующей по правилам традиционной многоразрядной арифметики. Ее ЦИ построены на основе умножителей,

Рис. 1. Структура квазипараллельного ЦИ, соответствующая первому алгоритму: RG – регистры, SM – сумматоры, CY – схема управления, CLK и ST – тактовый и стартовый сигналы соответственно

Рис. 2. Структура квазипараллельного ЦИ, соответствующая второму алгоритму

сумматоров и управляющего автомата. Применяются аппаратные методы ускорения арифметических операций 2-о порядка, для чего задействуются встроенные умножители кристалла *FPGA*. Это сократит потребление его логических ресурсов при высоком быстродействии рассматриваемой модели;

— модель ЦИС (ЦИС № 5), аналогичную предыдущей, но использующей для реализации умножителей только логические ресурсы микросхемы FPGA. Такую модель целесообразно реализовать также на бюджетных микросхемах, имеющих небольшое количество встроенных умножителей.

# 2. Экспериментальные исследования

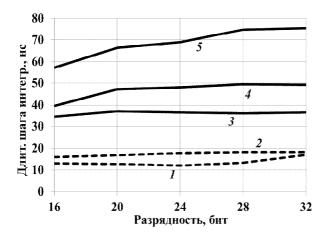

Модели ЦИС были синтезированы на базе микросхемы *FPGA Altera Stratix IV EP4SE*230*F*29*C*4 в САПР *Altera Quartus II Web Edition v*11.0. Описание схем проводилось на языке *VHDL*, синтез проводился с оптимизацией интегральных реализаций по быстродействию. Все модели ЦИС реализуют интерполяционные интегральные вычисления по формуле квадратичных парабол в 4-й симметричной избыточной системе счисления с цифрами {-2,...,2}. Шаг интегрирования в ЦИС № 1 и 2 длится 3 такта, в ЦИС № 3 − 9 тактов, в ЦИС № 4 и 5 − 7 тактов.

Получены зависимости (1 соответствует ЦИС № 2, 2 – ЦИС № 1, 3 – ЦИС № 3, 4 – ЦИС № 4, 5 – ЦИС № 5) длительностей шага интегрирования от эквивалентной 2-й разрядности вычислений для экспериментальной оценки и сравнения скоростных характеристик моделей ЦИС (рис. 3).

Рис. 3. Длительность шага интегрирования в ЦИС

Сравнение зависимостей 1, 2 с 3 показывает, что разработанный метод неавтономного вычисления интеграла способен до 2,5 раз ускорить квазипараллельные ЦИС по сравнению со случаем применения для их построения известного структурного метода. Сравнение этих зависимостей с 4 и 5 пока-

зывает, что это преимущество по сравнению с наиболее быстродействующими структурами ЦИС, применяющими параллельную многоразрядную арифметику, возрастает с увеличением точности интегральных вычислений примерно с 3 до 5 раз.

### Заключение

Результаты экспериментальных исследований быстродействия квазипараллельных ЦИС, использующих разработанный метод неавтономного вычисления интегрального приращения, согласуются с теоретическими оценками [4]. Они подтверждают эффективность внедрения при построении квазипараллельных ЦИС с целью существенного повышения их скоростных характеристик.

В дальнейшем предусматривается включение в подобные исследования программных реализаций традиционных ЦИС на современных платформах: многоядерных микропроцессорах, цифровых сигнальных процессорах и графических ускорителях с учетом других характеристик (энергопотребления, массогабаритных, стоимостных и др.)

# Литература

- 1. Лукин, Н. А. Функционально-ориентированные процессоры с однородной архитектурой для реализации алгоритмов бортовых систем управления [Текст] / Н. А. Лукин // Параллельные вычисления и задачи управления РАСО'2010: труды V Междунар. науч. конф., 26-28 окт. 2010 г. Москва, Россия, 2010. С. 1177-1185.

- 2. Беспалов, Д. А. Некоторые аспекты разработки современных цифровых интегрирующих вычислительных систем [Текст] / Д. А. Беспалов, В. Ф. Гузик // Известия южного федерального университета. Технические науки. — 2015. — № 3 (164). — С. 6-16.

- 3. Жабин, В. И. Реализация цифровых интеграторов на ПЛИС [Текст] / В. И. Жабин, Н. А. Ковалев // Проблеми інформатизації та управління. 2007. № 1 (19). С. 50-55.

- 4. Ковальов, М. О. Метод неавтономного обчислення інтегралу Стілт'єса [Текст] / М. О. Ковальов // Наукоємні технології - 2012 : тези наук.техн. конф. студентів та молодих учених, 12-16 лист. 2012 р. — Київ, Україна, 2012. — С. 26.

- 5. Пат. 80152 Україна, МПК<sup>6</sup> G 01 S 13/00, G 01 S 17/00, G 06 F 7/60. Цифровий інтегратор [Текст] / Жуков І. А., Ковальов М. О. ; заявник і патентовласник Національний авіаційний універсистет. и 2012 14548 ; заявл. 19.12.2012 ; опубл. 13.05.2013, Бюл. № 9. 10 с.

## References

- 1. Lukin, N. A. Funktsional'no-orientirovannye protsessory s odnorodnoi arkhitekturoi dlya realizatsii algoritmov bortovykh sistem upravleniya [Functionally-oriented Processors with Homogeneous Architecture for On-board Control System Algorithm Implementation]. Trudy V Mezhdunarodnoi nauchnoi konferentsii "Parallel'nye vychisleniya i zadachi upravleniya PACO'2010" [Proc. V Int. Conf. "Parallel Computations and Control Problems"]. Moscow, 2010, pp. 1177-1185 (In Russian).

- 2. Bespalov, D. A., Guzik, V. F. Nekotorye aspekty razrabotki sovremennykh tsifrovykh integriruyushchikh vychislitel'nykh sistem [Some Aspects of the Development of Modern Integrating Computer Sys-

- tems]. *Izvestiya yuzhnogo federal'nogo universiteta*. *Tekhnicheskie nauki*, 2015, no. 3 (164), pp. 6-16.

- 3. Zhabin, V. I., Kovalev, N. A. Realizatsiya tsi-frovykh integratorov na PLIS [Implementation of Digital Integrators on PLD]. *Problemi informatizatsii ta upravlinnya*, 2007, no. 1 (19), pp. 50-55.

- 4. Kovalov, M. O. Metod neavtonomnoho obchyslennia intehralu Stiltiesa [Method of Online calculating of Stieltjes integral]. *Tezy naukovo-tekhnichnoi konferentsii studentiv ta molodykh uchenykh "Naukoiemni tekhnolohii-2012"* [Abst. Conf. "High Tech-2012"]. Kyiv, 2012, p. 26 (In Ukrainian).

- 5. Zhukov, I. A., Kovalov, M. O. *Tsyfrovyi inte-hrator* [Digital Integrator]. Patent RF, № 80152, 2012.

Поступила в редакцию 12.03.2016, рассмотрена на редколлегии 14.04.2016

### ШВИДКОДІЯ ЦИФРОВИХ ІНТЕГРИРУЮЧИХ СТРУКТУР

## І. А. Жуков, М. О. Ковальов

Запропоновані алгоритми функціонування цифрових інтегруючих структур (ЦІС), що використовують розроблений метод неавтономного обчислення приросту інтеграла Стілт'єсу, і способи їх побудови. Проведені експериментальні дослідження швидкодії при реалізації їх на базі FPGA. Метод дозволяє забезпечити значну перевагу в швидкодії над квазіпаралельними ЦІС, побудованими з використанням відомого структурного методу, і ЦІС, що обчислюють за правилами паралельної багаторозрядної арифметики. Результати практичних досліджень підтверджують теоретичні оцінки і ефективність розробленого методу для значного прискорення інтегральних обчислень в ЦІС.

**Ключові слова:** цифрові інтегруючі структури, неавтономна арифметика (Online Arithmetic), надлишкові системи числення, швидкодія, апаратурна складність, FPGA.

# PERFORMANCE OF DIGITAL INTEGRATING STRUCTURES

### I. A. Zhukov, N. A. Kovalyov

Functional algorithms of digital integrating structures (DIS), that use the developeded method of on-line organization of Stieltjes integration, and its construction are offered. Experimental researches of DIS performance, implemented on FPGA basis, are made. The method ensures significant advantage in performance over quasiparallel DIS, that use known structural construct method, and DIS, that use parallel multi-bit arithmetic. Practical results confirm the theoretical assessments and the effectiveness of the developed method for the significant acceleration of integral calculation in DIS.

**Keywords:** digital integrating structures, Online Arithmetic, redundant number systems, performance, hardware complexity, FPGA.

**Жуков Игорь Анатольевич** – д-р техн. наук, проф., зав. каф. компьютерных систем и сетей Института компьютерных информационных технологий Национального авиационного университета, Киев, Украина, e-mail: zhuia@ukr.net.

**Ковалев Николай Александрович** – канд. техн. наук, ассистент кафедры компьютерных систем и сетей Института компьютерных информационных технологий Национального авиационного университета, Киев, Украина, e-mail: nikolay@onet.in.ua.

**Zhukov Igor Anatolievich** – Doctor of Technical Sciences, Professor, Head of Department of Computer Systems and Networks, Research Institute of Computer Information Technologies, National Aviation University, Kiev, Ukraine, e-mail: zhuia@ukr.net.

**Kovalyov Nikolay Alexandrovich** – Candidate of Technical Science, Assistant of Department of Computer Systems and Networks, Research Institute of Computer Information Technologies, National Aviation University, Kiev, Ukraine, e-mail: nikolay@onet.in.ua.