УДК 681.326:519.613

### В.И. ХАХАНОВ, Е.И. ЛИТВИНОВА, NGENE CHRISTOPHER UMERAH

Харьковский национальный университет радиоэлектроники

# СЕРВИСНОЕ ОБСЛУЖИВАНИЕ СОВРЕМЕННЫХ ЦИФРОВЫХ СИСТЕМ НА КРИСТАЛЛАХ

Рассматривается проблема адаптации технологий тестирования цифровых систем на кристаллах (System on Chip – SoC) для нового конструктивного поколения цифровых систем – System-in-Package (SiP), позволяющего эффективно и компактно имплементировать в кристаллы сверхсложные специализированные вычислительные и радиочастотные устройства для рынка электронных технологий. Вместе с тем пакет кристаллов формирует спектр новых задач сервисного обслуживания SiP-функциональностей в реальном масштабе времени, которое существенно отличается от процессов встроенного диагностирования SoC. В связи с этим предлагается алгебрологический метод диагностирования и восстановления работоспособности функциональных логических блоков FPGA, основанный на использовании таблиц неисправностей и их анализе в реальном масштабе времени.

**Ключевые слова**: дефект, тестирование, восстановление работоспособности, цифровая система на кристалле, программируемая логика.

#### Введение

За последние годы появились десятки работ, которые рассматривают вопросы, связанные с проблемой тестирования, диагностирования и ремонта цифровых систем на кристаллах и в пакетах (SoC, SiP). Особое место здесь занимает задача тестирования и ремонта логических компонентов цифровых систем, ввиду технологической сложности восстановления работоспособности логических элементов при возникновении в них дефектов. Существующие решения, предлагаемые в публикациях, сводятся к следующей классификации:

Дублирование логических элементов или областей кристалла, приводящее к удвоению аппаратной реализации функциональности. При фиксации неисправного элемента или области осуществляется переключение на исправный компонент с помощью мультиплексора [4]. Предложенные Xilinx модели FPGA (Field Programmable Gate Array) применимы также при ремонте компонентов FPGA от компании Altera. Основная единица измерения при ремонте — столбец или строка.

Использование генетических алгоритмов для диагностирования и восстановления работоспособности на основе автономной реконфигурации кристалла FPGA без использования внешних устройств управления [5]. Надежность диагностирования дефектов равна 99%, время ремонта — 36 миллисекунд вместо 660 секунд, необходимых для стандартного конфигурирования проекта.

Восстановление работоспособности кристаллов

FPGA, не критичное ко времени, путем замены локальных CLB на избыточные запасные компоненты предложено в [6,7]. Доступный уровень объединения CLB, подлежащий замене, для критически важных приложений составляет порядка тысячи логических элементов.

Технологии восстановления работоспособности логической части цифровых систем, имплементированных в кристаллы программируемой логики, основаны на существовании или внесении избыточности LUT-компонентов FPGA после выполнения процедур Place and Route. Физические дефекты кристалла, возникающие в процессе его изготовления или эксплуатации, проявляются как логические или временные и приводят к неправильному функционированию цифрового изделия. Дефекты привязываются не только к вентилям или LUT-компонентам, но и к конкретному месту на кристалле. Идея ремонта цифровой структуры сводится к исключению дефектного места при повторном выполнении процедур Place and Route после установления диагноза. При этом возможны две технологии ремонта: 1) Запрет дефектной области путем написания управляющих скриптов для достаточно длительной процедуры Place and Route, что не всегда приемлемо для цифровых систем, работающих в реальном масштабе времени. Однако такой подход приемлем и ориентирован на исключение дефектных областей любой кратности, имеющих место быть на кристалле. Запрет таких областей при повторном выполнении процедуры Place and Route приводит к восстановлению работоспособности. 2) Для цифровых систем реального времени выполнение процедуры Place and Route, направленной на восстановление работоспособности, может привести к катастрофическим последствиям. Необходим технологический подход, способный восстановить функциональность цифровой системы за миллисекунды, необходимые для перепрограммирования FPGA путем подачи нового битстрима, исключающего дефектные области из формирования функциональности. Такой подход основан на предварительной подготовке всех возможных битстримов, изолирующих будущие дефектные области путем их попадания в избыточную нефункциональную область кристалла. Чем больше резервная область, тем меньше число битстримов - проектных вариантов, привязанных к топологии, которое необходимо сгенерировать априори. Что касается кратных дефектов, не покрываемых одной резервной областью, здесь следует сегментировать цифровой проект, разбив его предварительно на непересекающиеся части, которые имеют собственные карты Place and Route. В данном случае можно ремонтировать цифровую систему, которая имеет для n распределенных на пластине дефектов n резервных сегментов. В этом случае общая площадь кристалла представляет сбой n+m одинаковых частей.

# 1. Технологии диагностирования блоков FPGA

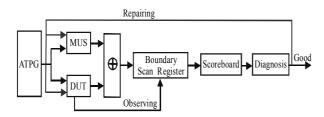

Основная роль в процессе диагностирования неисправных блоков FPGA отводится встроенной в кристалл инфраструктуре граничного сканирования, которая ориентирована на решение практически всех задач сервисного обслуживания SiPфункциональностей. Контроллер доступа обеспечивает мониторинг всех проблемных внутренних линий проекта с помощью регистра граничного сканирования, число разрядов которого должно соответствовать наперед заданной глубине диагностирования, а следовательно количеству блок LUT, клеток или кристаллов в SiP. Модель процесса сервисного обслуживания SiPфункциональности для диагностирования дефектов в компонентах кристаллов представлена на рис. 1.

Рис. 1. Модель процесса диагностирования F-IP

Здесь модуль функции Хог анализирует выходные реакции модели MUS и реального устройства

DUT на тестовые векторы, поступающие от встроенного генератора входных последовательностей. Блок Boundary Scan Register является мультизондом, предназначенным для мониторинга состояния всех блоков или клеток, далее компонентов кристалла. Модуль Scoreboard выполняет функцию анализа результатов мониторинга для диагностирования и последующего ремонта компонентов SoC. Результат диагностирования SiP представляет собой множество неисправных блоков, подлежащих исключению из функционального режима путем их замены на резервные компоненты.

Интересное решение задачи диагностирования может быть получено путем применения булевой алгебры для анализа таблицы неисправностей (ТН) М, представляющей собой декартово произведение теста Т на множество наперед заданных дефектов F. Вектор экспериментальной проверки V, равный по длине различимым тестовым сегментам, позволяет привести процедуру поиска дефектов к задаче покрытия, что дает максимально точный результат в виде ДНФ, где каждый терм есть возможный вариант наличия в устройстве подмножества или сочетания дефектов SiP. Модель процесса диагностирования представлена в следующем виде:

$$\begin{split} &A = < T, F, M, V>, \\ &T = (T_1, T_2, ..., T_i, ..., T_n); \ F = (F_1, F_2, ..., F_j, ..., F_m); \\ &M = \left| M_{ij} \right|, i = \overline{1, n}; j = \overline{1, m}; \ V = (V_1, V_2, ..., V_i, ..., V_n); \end{split}$$

$$V_i = R(T_i) \oplus R^*(T_i); \ \{V_i, T_i, M_{ij}, F_j\} \in \{0, 1\}.$$

Значение координаты вектора V есть результат выполнения операции Хог над обобщенной модельной и фактической реакцией выходов устройства. Если хотя бы на одном выходе устройства зафиксировано единичное значение вектора V на і-том тестовом сегменте, то обобщенное состояние выхода равно 1. В противном случае значение координаты вектора V равно 0.

# 1.1. Алгебро-логический метод диагностирования неисправностей

Решение задачи диагностирования сводится к анализу таблицы неисправностей, полученной в результате моделирования дефектов компонентов SiP, путем записи логического произведения дизъюнкций строк таблицы неисправностей, записанных по единичным значениям вектора экспериментальной проверки:

$$F = \bigwedge_{\forall V_i = 1}^{i = \overline{l,n}} (\bigvee_{\forall M_{ii} = 1}^{j = \overline{l,m}} F_j).$$

(2)

Конъюнктивная нормальная форма (КНФ), полученная из TH, трансформируется к дизъюнктив-

ной нормальной форме (ДНФ) с помощью эквивалентных преобразований (логическое умножение, минимизация и поглощение). В результате получается булева функция, где термы – логические произведения представляют полное множество решений в виде сочетания дефектов (дающих по выходам SiP или ее компонентам двоичные координаты вектора экспериментальной проверки V):

$$F = \bigwedge_{\forall V_i = 1}^{i = \overline{l, n}} (\bigvee_{\forall M_{ij} = 1}^{j = \overline{l, m}} F_j) = \begin{vmatrix} a \lor ab = b \\ a \lor a = a \end{vmatrix} = \bigvee_{i = 1}^{2^m} (\bigwedge_{j = 1}^m k_j F_j), k_j = \{0, 1\}. (3)$$

Функция (3) в общем случае формирует диагноз в виде некоторого подмножества сочетаний (кратных) дефектов, которые далее нуждаются в уточнении путем применения дополнительного зондирования внутренних точек с помощью регистра граничного сканирования. Количество единиц в векторе экспериментальной проверки V формирует число дизъюнктивных термов КНФ (3).

Каждый терм — построчная запись дефектов (через логическую операцию ИЛИ), оказывающих влияние на выходы функциональности. Представление таблицы в виде аналитической записи — конъюнктивной нормальной формы дает потенциальную возможность существенно сократить объем диагностической информации для поиска дефектов.

Последующее преобразование КНФ к ДНФ на основе тождеств алгебры логики позволяет существенно уменьшить булеву функцию.

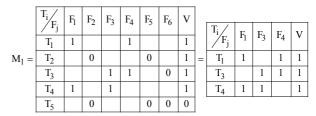

Алгебрологический метод рассматривается на примере таблицы неисправностей М1 и представлен в виде следующих пунктов алгоритма [8,10].

|         | $T_i / F_j$    | F <sub>l</sub> | F <sub>2</sub> | F <sub>3</sub> | F <sub>4</sub> | F <sub>5</sub> | F <sub>6</sub> | V |

|---------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|

|         | T <sub>1</sub> | 1              |                |                | 1              |                |                | 1 |

| $M_1 =$ | T <sub>2</sub> |                | 1              |                |                | 1              |                | 1 |

|         | T <sub>3</sub> |                |                | 1              | 1              |                | 1              | 1 |

|         | T <sub>4</sub> | 1              |                | 1              |                |                |                | 1 |

|         | T <sub>5</sub> |                | 1              |                |                | 1              | 1              | 0 |

- 1. Определение строк таблицы неисправностей, соответствующих нулевым значениям вектора экспериментальной проверки в целях обнуления единичных координат найденных строк. В данном случае это одна строка Т5.

- 2. Нахождение всех столбцов, которые имеют нулевые значения координат строк с нулевым состоянием ВЭП. Обнуление единичных значений найденных столбцов. В данном случае: F2, F5, F6.

- 3. Удаление из таблицы неисправностей строк и столбцов, имеющих только нулевые значения координат (найденные в пунктах 1 и 2).

4. Построение КНФ по единичным значениям ВЭП. Преобразование КНФ к ДНФ с последующей минимизацией функции:

$$\begin{split} F &= (F_1 \vee F_4) \wedge (F_3 \vee F_4) \wedge (F_1 \vee F_3) = \\ &= (F_1 F_3 \vee F_3 F_4 \vee F_1 F_4 \vee F_4 F_4) \wedge (F_1 \vee F_3) = \\ &= F_1 F_1 F_3 \vee F_1 F_3 F_4 \vee F_1 F_1 F_4 \vee F_1 F_4 F_4 \vee F_1 F_3 F_3 \vee \\ \vee F_3 F_3 F_4 \vee F_1 F_3 F_4 \vee F_3 F_4 F_4 = \\ &= F_1 F_3 \vee F_1 F_3 F_4 \vee F_1 F_4 \vee F_3 F_4 \vee F_1 F_3 F_4 \vee F_3 F_4 = \\ &= F_1 F_3 \vee F_1 F_4 \vee F_3 F_4. \end{split}$$

Предложенный алгоритм ориентирован на анализ таблицы неисправностей в целях уменьшения объема ТН и последующих вычислений, связанных с построением ДНФ, которая формирует все решения по установлению диагноза функциональностей SoC. Дальнейшее уточнение диагноза возможно только с применением мультизонда на основе регистра граничного сканирования данных.

# 1.2. Векторно-логический метод диагностирования неисправностей

Обработка ТН для получения диагноза выполняется по сценарию, основанному на использовании векторных операций конъюнкции, дизъюнкции и отрицания над стоками таблицы неисправностей. Аналитическая векторно-логическая модель диагностирования кратных дефектов определяется конъюнкцией двух компонентов, где первый есть дизъюнкция векторов, соответствующих единичным координатам ВЭП, а второй – инверсия дизъюнкций векторов соответствующих нулевым координатам ВЭП:

$$F = M^{1} \wedge \overline{M}^{0} = \left( \bigvee_{V_{i}=1} M_{i} \right) \wedge \left( \overline{\bigvee_{V_{i}=0} M_{i}} \right). \tag{4}$$

Модель диагностирования одиночных дефектов отличается выполнением на первом шаге сценария операции конъюнкции (вместо дизъюнкции) всех векторов, соответствующих единичным координатам ВЭП:

$$F = M^{1} \wedge \overline{M}^{0} = \left( \bigwedge_{V_{i}=1} M_{i} \right) \wedge \left( \overline{\bigvee_{V_{i}=0} M_{i}} \right). \tag{5}$$

Пример 1. Выполнить диагностирование кратных дефектов в структуре SiP векторно-логическим методом, для которой заданы таблица неисправностей и вектор экспериментальной проверки:

(6)

| $T_i / F_j$                 | F <sub>l</sub> | F <sub>2</sub> | F <sub>3</sub> | F <sub>4</sub> | F <sub>5</sub> | F <sub>6</sub> | F <sub>7</sub> | F <sub>8</sub> | F9 | F <sub>10</sub> | V |

|-----------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|-----------------|---|

| T <sub>1</sub>              |                |                |                | 1              |                |                |                |                |    | 1               | 1 |

| T <sub>2</sub>              |                | 1              |                |                |                |                | 1              |                |    |                 | 0 |

| T <sub>3</sub>              |                |                | 1              |                |                | 1              |                |                | 1  |                 | 0 |

| T <sub>4</sub>              | 1              |                |                |                |                |                |                |                |    |                 | 0 |

| T <sub>5</sub>              |                |                |                |                | 1              |                |                | 1              |    |                 | 1 |

| T <sub>6</sub>              | 1              | 1              |                |                |                |                |                |                |    |                 | 0 |

| T <sub>7</sub>              |                |                | 1              |                |                |                |                |                |    |                 | 0 |

| T <sub>8</sub>              |                |                |                | 1              |                |                |                |                |    |                 | 1 |

| T <sub>9</sub>              |                |                |                |                | 1              | 1              |                |                |    |                 | 0 |

| T <sub>10</sub>             |                |                |                |                |                |                | 1              |                |    |                 | 0 |

| T <sub>11</sub>             |                |                |                |                |                |                |                | 1              | 1  | 1               | 1 |

| M <sup>1</sup>              |                |                |                | 1              | 1              |                | <u> </u>       | 1              | 1  | 1               | 1 |

| M <sup>0</sup>              | 1              | 1              | 1              |                | 1              | 1              | 1              |                | 1  |                 | 0 |

| $\overline{\overline{M}}^0$ | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 1              | 0  | 1               | 1 |

| F                           | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 1              | 0  | 1               | 1 |

Обработка таблицы неисправностей в соответствии с формулой (4) дает результат, представленный в четырех нижних строках (6). Последняя строка таблицы неисправностей фиксирует факт наличия в схеме дефектов, представленных в векторной или теоретико-множественной форме

$F = (0001000101) = \{F_4, F_8, F_{10}\}$ .

Для преобразования полученного решения к ДНФ кратных дефектов используется структура ТН, маскируемая вектором F, представленным последней строкой таблицы:

$$F = M^{1} \wedge F = \bigwedge_{V_{i}=1} (M_{i} \wedge F). \tag{7}$$

Полученные векторы, число которых в пределе равно количеству единиц ВЭП, логически перемножаются. При этом каждый вектор может быть компактно записан в виде дизъюнкции значений единичных координат. Для представленной выше ТН применение формулы (7) дает следующий результат:

$$\begin{split} &F = (F_4 \vee F_{10})(F_8)(F_4)(F_4 \vee F_{10}) = \\ &= F_4 F_8 F_4 F_4 \vee F_{10} F_8 F_4 F_4 \vee F_4 F_8 F_4 F_{10} \vee F_{10} F_8 F_4 F_{10} = \\ &= F_4 F_8 \vee F_{10} F_8 F_4 \vee F_4 F_8 F_{10} \vee F_{10} F_8 F_4 = F_4 F_8. \end{split}$$

Он интересен тем, что благодаря записи дефектов в виде термов ДНФ, покрывающих все единичные координаты ВЭП, появилась возможность исключить дефект  $F_{10} \in F$  из списка неисправностей.

Преимущество векторно-логического метода заключается в технологичности анализа таблицы неисправностей, вычислительная сложность которого имеет мультипликативную зависимость от числа дефектов и мощности теста:  $Q = n \times m$ . Метод следует использовать при преобладании в таблице неисправностей единичных координат, когда алгебрологический метод дает высокую оценку по Квайну сложности ДНФ и КНФ. Недостаток заключается в невозможности представления всех сочетаний дефектов, формирующих термы для покрытия единичных координат вектора экспериментальной проверки.

#### Заключение

Предложенные методы диагностирования: алгебрологический и векторно-логический предлагают специалисту в области проектирования и тестирования цифровых систем на кристаллах математический аппарат, который способен осуществить диагноз дефектных компонентов на основе использования предварительно построенной таблицы неисправностей. При этом векторные решения, эффективно полученные векторно-логическим методом, можно представлять всеми возможными сочетаниями дефектов в виде термов ДНФ, что характерно для алгебрологического метода. Второй метод эффективен при числе единиц в матрице неисправностей, превышающем 10-20%.

# Литература

- 1. Kwang-Ting C. The Need for a SiP Design and Test Infrastructure / C. Kwang-Ting // IEEE Design and Test of Computers. – May–June, 2006. – P. 181.

- 2. Fontanelli A. System-in-Package Technology: Opportunities and Challenges / A. Fontanelli // Quality Electronic Design, 2008.- ISQED 2008, 9th International Symposium. – March, 2008. – P. 589-593.

- 3. Appello D. System-in-package testing: problems and solutions / D. Appello, P. Bernardi, M. Grosso, M.S. Reorda // IEEE Design & Test of Computers.— Vol. 23, Issue 3.– May-June, 2006.– P. 203-211.

- 4. Subhasish M. Reconfigurable architecture for autonomous self-repair / M. Subhasish, W.-J. Huang, N.R. Saxena, E.J. McCluskey // IEEE Design & Test of Computers. – Volume 21, Issue 3. – May-June, 2004. – P. 228-240.

- 5. Ross R. A FPGA Simulation Using Asexual Genetic Algorithms for Integrated Self-Repair / R. Ross, R. Hall // Adaptive Hardware and Systems, 2006.- AHS 2006. – First NASA/ESA Conference on Volume. – Issue 15-18 June 2006.- P. 301-304.

- 6. Habermann S. Built-in self repair by reconfiguration of FPGAs / S. Habermann, R. Kothe, H.T. Vierhaus // Proceedings of the 12th IEEE International Symposium on On-Line Testing. - 2006. - P. 187-188.

- 7. Pontarelli S. Reliability Evaluation of Repairable/Reconfigurable FPGAs / S. Pontarelli, M. Ottavi, V. Vankamamidi, A. Salsano, F. Lombardi // 21st IEEE International Symposium on Defect and Fault-Tolerance in VLSI Systems (DFT'06) .- October, 2006.-P. 227-235.

- 8. Парфентий А.Н. Модели инфраструктуры сервисного обслуживания цифровых систем на кристаллах / А.Н. Парфентий, В.И. Хаханов, Е.И. Лит-

винова // ACV и приборы автоматики.— Вып. 138.— 2007.— C.83-99.

9. Hahanov V. Diagnosis and repair method of SoC memory/ V. Hahanov, A. Hahanova, S. Chumachenko, S. Galagan // WSEAS transactions on

circuits and systems.— Vol.7.— 2008.— P. 698-707. 10. Hahanov V. Algebra-logical diagnosis model for SoC F-IP / V. Hahanov, V. Obrizan, E. Litvinova, Ka Lok Man. // WSEAS transactions on circuits and systems.—

*Vol.* 7.– 2008.– *P.* 708-717.

Поступила в редакцию 12.02.2008

**Рецензент:** д-р техн. наук, проф., А.А. Мельник заведующий кафедрой ЭВМ, Национальный университет «Львовская политехника», Львов, Украина.

### СЕРВІСНЕ ОБСЛУГОВУВАННЯ СУЧАСНИХ ЦИФРОВИХ СИСТЕМ НА КРИСТАЛАХ

#### В.І. Хаханов, Е.І. Литвинова, Ngene Christopher Umerah

Запропоновано алгебрологічний та векторно-логічний методи діагностування, призначені для нового конструктивного покоління цифрових систем на кристалах — System-in-Package і основані на використанні заздалегідь побудованої таблиці несправностей. Розроблено алгебрологічний метод відновлення працездатності функціональних логічних блоків FPGA на основі вирішення задачі покриття, орієнтований на імплементацію в кристал в якості одного з компонентів інфраструктури сервісного обслуговування (І-ІР). Метод дозволяє знайти точне та оптимальне рішення, у вигляді мінімальної кількості резервних блоків, необхідних для відновлення працездатності логічних блоків кристалу FPDA, при наявності дефектів будь-якої кратності

**Ключові слова:** дефект, тестування, відновлення працездатності, цифрова система на кристалі, програмовна логіка.

#### INFRASTRUCTURE IP FOR RECENT DIGITAL SYSTEMS-ON-CHIPS

#### V.I. Hahanov, E.I. Litvinova, Ngene Christopher Umerah

Algebra-logical and vector-logical diagnosis methods for new generation of digital system-on-a-chip – system-in-package are proposed. They are based on use the fault detection table. Algebra-logical repair method for FPGA functional logical blocks is developed. It is based on solving the coverage problem and oriented on hardware implementation to a silicon chip as a component of Infrastructure IP. A method allows obtaining an exact solution in the form of minimal quantity of spares, which are necessary to repair of FPGA logical blocks under faults of all multiplicity.

Key words: fault, test, repair, system-on-a-chip, programmable logic.

**Хаханов Владимир Иванович** - д-р техн. наук, профессор кафедры АПВТ Харьковского национального университета радиоэлектроникиЭ, декан факультета КИУ ХНУРЭ, Харьков, Украина, e-mail: hahanov@kture.kharkov.ua.

**Литвинова Евгения Ивановна** – к.т.н., доцент, доцент кафедры технологии и автоматизации производства РЭС и ЭВС Харьковского национального университета радиоэлектроники, Харьков, Украина.

Ngene Christopher Umerah - аспирант кафедры АПВТ Харьковского национального университета радиоэлектроники, Харьков, Украина.