УДК 681.234

# A.A. БАРКАЛОВ<sup>1</sup>, Л.А. ТИТАРЕНКО<sup>1</sup>, С.А. ЦОЛОЛО<sup>2</sup>

<sup>1</sup>University of Zielona Gora, Poland

## УМЕНЬШЕНИЕ АППАРАТУРНЫХ ЗАТРАТ В СХЕМЕ МИКРОПРОГРАММНОГО АВТОМАТА МУРА НА СРLD

Предлагается метод оптимизации аппаратурных затрат в логической схеме автомата Мура, реализуемого в базисе CPLD. Метод основывается на наличии классов псевдоэквивалентных состояний автомата Мура и большом коэффициенте объединения по входу макроячеек PAL. Приведен пример применения предложенного метода.

## микропрограммный автомат Мура, ПЛИС, CPLD, макроячейка, PAL, оптимизация

#### Введение

Устройство управления является важной частью любой цифровой системы [1]. На практике достаточно часто используется модель микропрограммного автомата (МПА) Мура [2]. В настоящее время для реализации схем МПА широко используются программируемые логические устройства типа CPLD (complex programmable logic devices) [3 – 5]. B основе CPLD находятся макроячейки PAL (programmable array logic), характеризующиеся большим коэффициентом объединения по входу (несколько десятков) и ограниченным числом конъюнктивных термов (до десяти). Одной из актуальных задач, возникающих при синтезе схемы автомата Мура с использованием CPLD, является уменьшение аппаратурных затрат, то есть числа макроячеек РАL в схеме автомата [4, 5]. Решение этой задачи позволяет уменьшить количество микросхем, что улучшает такие параметры, как быстродействие, надежность, стоимость и потребляемая мощность [1, 4]. Для успешного решения этой задачи необходимо учитывать как особенности модели автомата, так и особенности CPLD. К особенностям модели автомата Мура относятся наличие псевдоэквивалентных состояний и зависимость выходных сигналов только от состояний [6, 7].

Целью данного исследования является оптимизация комбинационной схемы автомата Мура за счет обобщенного кодирования состояний и их классов, а также использование нескольких источников кода состояний, что возможно благодаря особенностям СРLD. Задачей исследования является разработка формализованного метода синтеза МПА Мура, позволяющего оптимизировать число макроячеек РАL в схемах блоков формирования функций возбуждения памяти и микроопераций.

#### 1. Общие положения

Пусть автомат Мура задан прямой структурной таблицей (ПСТ) [2] со столбцами:  $a_m$  – исходное состояние, входящее в множество состояний  $A=\{a_1,...,a_M\}$  ;  $K(a_m)$  – код состояния  $a_m\in A$  разрядности

$$R = \lceil \log_2 M \rceil; \tag{1}$$

$a_s$  — состояние перехода;  $K(a_s)$  — код состояния  $a_s \in A$  ;  $X_h$  — конъюнкция входных сигналов (логических условий), входящих в множество  $X = \{x_1,...,x_L\}$  , которая определяет переход  $a_m,a_s>$  ;  $\Phi_h$  — набор функций возбуждения памяти, входящих во множество  $\Phi=\{D_1,...,D_R\}$  и

$<sup>^2</sup>$ Донецкий национальный технический университет, Украина

принимающих единичное значение для переключения памяти из  $K(a_m)$  в  $K(a_s)$ ; h=1,...,H — номер перехода. Кроме того, в столбце  $a_m$  записывается выходной набор  $Y(a_m)\subseteq Y$ , формируемый в состоянии  $a_m$ . Здесь  $Y=\{y_1,...,y_N\}$  — множество микроопераций. Эта таблица является основой для формирования систем булевых функций:

$$\Phi = \Phi(T, X); \tag{2}$$

$$Y = Y(T). (3)$$

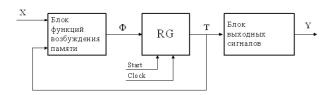

В системах (2)-(3) множество  $T = \{T_1, ..., T_R\}$  включает внутренние переменные, используемые для кодирования состояний МПА. Системы (2)-(3) определяют структурную схему МПА Мура  $U_1$  (рис. 1).

Рис. 1. Структурная схема автомата Мура  $U_1$

В структуре  $U_1$  блок функций возбуждения памяти (БФП) реализует систему (2), а блок выходных сигналов (БВС) реализует систему (3). Схемы обоих блоков реализуются на макроячейках PAL. Память автомата представлена регистром RG, который обнуляется по сигналу Start. Периодический сигнал Clock используется для синхронизации работы схемы. Для уменьшения числа макроячеек PAL в схеме блока БВС можно использовать метод специального кодирования состояний, ориентированный уменьшение числа термов  $Q(y_n)$  в каждой из функций  $y_n \in Y$  [9]. При этом возможно уменьшение числа уровней в комбинационной схеме блока БВС, что уменьшает длительность такта работы МПА. В предельном случае общее число макроячеек в блоке БВС равняется числу микроопераций N . Однако специальное кодирование состояний не ориентировано на уменьшение аппаратурных затрат в блоке БФП. Для решения этой задачи необходимо применить метод оптимального кодирования состояний, использующий наличие классов псевдоэквивалентных состояний  $B_i \in \Pi_A$  с мощностью, большей двух [8, 9]. Состояния  $a_m, a_p \in A$  называются псевдоэквивалентными, если ими отмечены операторные вершины алгоритма управления [2], выходы которых соединены со входом одной и той же вершины алгоритма. Такие состояния относятся к одному классу разбиения  $\Pi_A = \{B_1, ..., B_I\}$  множества состояний, основанному на отношении псевдоэквивалентности [8]. При оптимальном кодировании каждый класс  $B_i \in \Pi_A$  представляется минимально возможным числом обобщенных интервалов R -мерного булева пространства, а пределе – одним. При этом длина ПСТ (число строк в ней) может быть уменьшено до величины  $H_0$ , определяемой числом переходов эквивалентного автомата Мили. Для специального или оптимального кодирования состояний может быть использован, например, известный алгоритм ESPRESSO [1]. Рассмотренные методы кодирования состояний не позволяют одновременно уменьшить число макроячеек PAL в схемах блоков БФП и БВС до минимально возможных значений. В настоящей работе предлагается метод синтеза, позволяющий решить эту задачу. Метод основан на наличии псевдоэквивалентных состояний и зависимости микроопераций только от состояний (особенности модели автомата) и значительном числе входов макроячеек PAL (особенности базиса CPLD).

#### 2. Основная идея предлагаемого метода

Используем разбиение  $\Pi_A$  для формирования системы булевых функций

$$B_i = \bigvee_{m=1}^{M} C_{im} a_m (i = 1, ..., I),$$

(4)

где  $C_{im}$  — булева переменная, равная единице, если и только если  $a_m \in B_i$  . Закодируем состояния

$a_m \in A$  таким образом, чтобы каждая функция систем (3) и (4) выражалась минимально возможным обобщенных интервалов R-мерного булева пространства. Назовем такой подход обобщенным кодированием состояний, для реализации которого может быть использован алгоритм ESPRESSO [1].

Разобьем множество  $\Pi_A$  на классы  $\Pi_B$  и  $\Pi_C$  , при этом  $B_i\!\in\!\Pi_B$  , если

$$K_i = 1, (5)$$

где  $K_i$  — число интервалов, представляющих класс  $B_i \in \Pi_A$ . Закодируем классы  $B_i \in \Pi_C$  двоичными кодами  $K(B_i)$  разрядности

$$R_1 = \lceil \log_2(I_c + 1) \rceil, \tag{6}$$

где  $I_C = |\Pi_C|$  . Используем для такого кодирования переменные  $\tau_r \in \tau$  , где  $|\tau| = R_1$  . Теперь может быть сформирована система функций

$$\tau = \tau(T) \ . \tag{7}$$

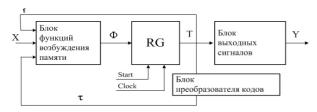

В этом случае автомат Мура может быть представлен структурной схемой  $U_2$  (рис. 2).

Рис. 2. Структурная схема автомата Мура  $U_2$

В МПА  $U_2$  переменные из множества T представляют коды  $C(B_i)$  классов  $B_i$   $\in$   $\Pi_B$  , а переменные из множества  $\tau$  — коды  $K(B_i)$  классов  $B_i$   $\in$   $\Pi_C$  . Блок БФП реализует систему функций

$$\Phi = \Phi(T, \tau, X), \tag{8}$$

блок БВС – систему (3), а блок преобразователя кодов (БПК) – систему (7). Таким образом, блок БПК реализует преобразование кодов, представляющих состояния  $a_m \in B_i$ , в код  $K(B_i)$  класса  $B_i \in \Pi_C$ . Такой подход позволяет уменьшить число термов,

реализуемых в блоке БФП, до  $H_0$  и уменьшить число макроячеек PAL в блоке БВС (в пределе до N) по сравнению с оптимальным кодированием состояний. Однако оптимизация связана с введением блока БПК, потребляющего некоторые ресурсы кристалла. Этот блок может быть исключен при выполнении условия

$$I_c = 0. (9)$$

В настоящей работе предлагается метод синтеза автомата Мура  $U_2$  , включающий следующие этапы:

- 1. Формирование разбиения  $\Pi_A$  и системы функций (4).

- 2. Обобщенное кодирование состояний  $a_m \in A \, .$

- 3. Формирование множеств  $\Pi_B$  и  $\Pi_C$ .

- 4. Кодирование классов  $B_i \in \Pi_C$  и формирование системы функций (7).

- 5. Формирование системы функций (3).

- 6. Формирование прямой структурной таблицы автомата  $U_2$  и системы (8).

- 7. Синтез логической схемы автомата  $U_2$  в заданном элементном базисе.

# 3. Пример применения предложенного метода

Пусть ПСТ автомата Мура  $S_1$  построена на основе следующей системы обобщенных формул перехода [9]:

$$B_{1} \to x_{1}a_{2} \vee \bar{x}_{1}a_{3};$$

$$B_{2} \to x_{2}a_{4} \vee \bar{x}_{2}x_{3}a_{5} \vee \bar{x}_{2}\bar{x}_{3}a_{6};$$

$$B_{3} \to x_{3}a_{6} \vee \bar{x}_{3}x_{4}a_{8} \vee \bar{x}_{3}\bar{x}_{4}a_{1};$$

$$B_{4} \to x_{5}a_{8} \vee \bar{x}_{5}x_{6}a_{11} \vee \bar{x}_{5}\bar{x}_{6}a_{13};$$

$$B_{5} \to a_{10};$$

$$B_{6} \to x_{1}a_{12} \vee \bar{x}_{1}a_{1};$$

$$B_{7} \to x_{4}a_{1} \vee \bar{x}_{4}x_{5}a_{7} \vee \bar{x}_{4}\bar{x}_{5}x_{6}a_{11} \vee \bar{x}_{4}\bar{x}_{5}\bar{x}_{6}a_{13}.$$

$$(10)$$

Пусть при этом получено разбиение  $\Pi_A = \{B_1,...,B_7\}$ , где  $B_1 = \{a_1\}$ ,  $B_2 = \{a_2,a_3\}$ ,  $B_3 = \{a_4\}$ ,  $B_4 = \{a_5,a_6,a_7\}$ ,  $B_5 = \{a_8,a_9\}$ ,  $B_6 = \{a_{10}\}$ ,  $B_7 = \{a_{11},a_{12},a_{13}\}$ . Пусть система микроопераций автомата  $S_1$  представляется следующей системой уравнений:

$$y_{1} = a_{2} \lor a_{3} \lor a_{12}; y_{2} = a_{4} \lor a_{8} \lor a_{9} \lor a_{10};$$

$$y_{3} = a_{3} \lor a_{7} \lor a_{8} \lor a_{11}; y_{4} = a_{5} \lor a_{11};$$

$$y_{5} = a_{6} \lor a_{7} \lor a_{8}; y_{6} = a_{4} \lor a_{6} \lor a_{10};$$

$$y_{7} = a_{3} \lor a_{11} \lor a_{12} \lor a_{13}; y_{8} = a_{3} \lor a_{7} \lor a_{12}.$$

$$(11)$$

Итак, для автомата  $S_1$  имеем M=13 , R=4 ,  $T=\{T_1,...,T_4\}\ ,\ \varPhi=\{D_1,...,D_4\}\ ,\ I=7\ ,\ N=8\ .$

Сформируем систему (4), которая имеет следующий вид:

$$B_{1} = a_{1}$$

;  $B_{2} = a_{2} \vee a_{3}$ ;

$B_{3} = a_{4}$ ;  $B_{4} = a_{5} \vee a_{6} \vee a_{7}$ ;

$B_{5} = a_{8} \vee a_{9}$ ;  $B_{6} = a_{10}$ ;

$B_{7} = a_{11} \vee a_{12} \vee a_{13}$ . (12)

Результат обобщенного кодирования состояний для автомата  $S_1$  показан картой Карно на рис. 3.

|    | 00                    | 01                    | 11                    | 10              |

|----|-----------------------|-----------------------|-----------------------|-----------------|

| 00 | $\mathbf{a_1}$        | a <sub>2</sub>        | *                     | a <sub>4</sub>  |

| 01 | <b>a</b> <sub>5</sub> | *                     | $\mathbf{a}_6$        | a <sub>10</sub> |

| 11 | a <sub>11</sub>       | <b>a</b> <sub>3</sub> | <b>a</b> <sub>7</sub> | a <sub>8</sub>  |

| 10 | a <sub>13</sub>       | a <sub>12</sub>       | *                     | <b>a</b> 9      |

Рис. 3. Коды состояний автомата Мура  $S_1$

Анализ этой карты показывает, что классы  $B_1, B_3, B_5, B_6 \in \Pi_B$  и  $B_2, B_4, B_7 \in \Pi_C$ . Таким образом,  $I_{\tilde{N}} = 3$ ,  $R_1 = 2$ ,  $\tau = \{\tau_1, \tau_2\}$ . Закодируем классы  $B_i \in \Pi_C$  следующим образом:  $K(B_2) = 11$ ,  $K(B_4) = 01$ ,  $K(B_7) = 10$ . Таким образом, чем больше состояний входит в класс  $B_i \in \Pi_C$ , тем меньше единиц содержит код этого класса. Отметим, что код 00 соответствует ситуации  $B_i \in \Pi_B$ .

Этим объясняется наличие единицы в формуле (6). Из карты Карно имеем  $C(B_1) = 0000$ ,  $C(B_3) = 001*$ ,  $C(B_5) = 1*10$ ,  $C(B_6) = 0110$ .

Сформируем систему уравнений (7). Например,  $K(B_4) = 01$  и коды состояний  $a_m \in B_4$  входят в два обобщенных интервала 010\* и \*111. Следовательно, булево уравнение для переменной  $\tau_2$  содержит термы  $\overline{T}_1T_2\overline{T}_3$  и  $T_2T_3T_4$ . Выполняя подобные действия, получим систему функций блока БПК:

$$\tau_{1} = \overline{T}_{1}\overline{T}_{2}T_{3} \vee T_{2}\overline{T}_{2}T_{3} \vee T_{1}\overline{T}_{3}\overline{T}_{4} \vee T_{1}\overline{T}_{2}\overline{T}_{3};$$

$$\tau_{2} = \overline{T}_{1}\overline{T}_{2}T_{3} \vee T_{2}\overline{T}_{2}T_{3} \vee \overline{T}_{1}T_{2}\overline{T}_{3} \vee T_{2}T_{3}T_{4}.$$

(13)

Используя систему (11) и коды из рис. 3, получим систему функций блока БВС:

$$y_1 = \overline{T_3} T_4;$$

$y_2 = T_3 \overline{T_4};$   $y_3 = T_1 T_2;$

$y_4 = T_2 T_3 \overline{T_4};$   $y_5 = T_2 T_3;$   $y_6 = \overline{T_1} T_3;$  (14)

$y_7 = T_1 \overline{T_3};$   $y_8 = T_1 T_4.$

Преобразованная ПСТ автомата  $S_1$  строится по системе (10) и включает столбцы  $B_i$ ,  $C(B_i)$ ,  $K(B_i)$ ,  $a_s$ ,  $K(a_s)$ ,  $X_h$ ,  $\Phi_h$ , h. Фрагмент преобразованной ПСТ для классов  $B_1, B_2 \in \Pi_A$  содержит 5 строк (табл. 1).

| $B_i$ | $C(B_i)$ | $K(B_i)$ | $a_s$ | $K(a_s)$ | $X_h$                | $\Phi_h$          | h |

|-------|----------|----------|-------|----------|----------------------|-------------------|---|

| $B_1$ | 0000     | 00       | $a_2$ | 0001     | $x_1$                | $D_4$             | 1 |

|       |          |          | $a_3$ | 1101     | $\bar{x}_1$          | $D_1D_2D_4$       | 2 |

| $B_2$ | ****     | 11       | $a_4$ | 0010     | $x_2$                | $D_3$             | 3 |

|       |          |          | $a_5$ | 0100     | $\bar{x}_2x_3$       | $D_2$             | 4 |

|       |          |          | $a_6$ | 0111     | $\bar{x}_2\bar{x}_3$ | $D_{2}D_{3}D_{4}$ | 5 |

Связь этой таблицы с системой (10) и кодами классов и состояний очевидны. Отметим, что при  $B_i \in \Pi_B$  столбец  $K(B_i)$  содержит код 00, а при  $B_i \in \Pi_C$  содержимое столбца  $C(B_i)$  игнорируется и может быть любым, что отмечено знаками \*. Эта таблица является основой для формирования системы (8). Например, из табл. 1 с учетом минимизации имеем:

$$\begin{split} D_1 &= \overline{T_1} \overline{T_2} \overline{T_3} \overline{T_4} \ \overline{\tau_1} \overline{\tau_2} \ \overline{x_1} \text{ (строка 2)}; \\ D_2 &= \overline{T_1} \overline{T_2} \overline{T_3} \overline{T_4} \ \overline{\tau_1} \overline{\tau_2} \ \overline{x_1} \vee \tau_1 \tau_2 \overline{x_2} \text{ (строки 2,4,5)}; \\ D_3 &= \tau_1 \tau_2 x_2 \vee \tau_1 \tau_2 \overline{x_3} \text{ (строки 3,5)}; \\ D_4 &= \overline{T_1} \overline{T_2} \overline{T_3} \overline{T_4} \ \overline{\tau_1} \overline{\tau_2} \ \overline{x_1} \vee \tau_1 \tau_2 \overline{x_2} \overline{x_3} \text{ (строки 1,2,5)}. \end{split}$$

Реализация схемы автомата  $S_1$  сводится к реализации систем функций (13, 14, 15) на элементах РАL, что может быть выполнено, например, с использованием пакета WebPack [9].

Отметим, что для модели  $U_2$  длина преобразованной ПСТ всегда равняется  $H_0$ . Так, для автомата  $S_1$  имеем  $H_0=18$ . Эта величина совпадает с числом термов в системе (9). Отметим, что для автомата  $S_1$  H=36, что определяется из выражения

$$H = \sum_{i=1}^{I} M_i H_i \ . \tag{16}$$

В выражении (16) параметр  $M_i = \left| B_i \right|$ , а параметр  $H_i$  равен числу термов в формуле перехода для класса  $B_i \in \Pi_A$ . Для автомата  $S_1$  (модель  $U_2$ ) число термов в системе (3) равняется 8, что совпадает с числом микроопераций N. Для реализации схемы блока БПК необходимо реализовать 8 термов системы (12). Таким образом, общее число реализуемых термов для модели  $U_2$  равняется 32.

Отметим, что для модели  $U_1$  это число равняется 62. При специальном кодировании состояний число термов в системе (2) равняется  $28 > H_0$ .

Таким образом, в этом случае необходимо реализовать 36 термов. Естественно, что число макроячеек PAL зависит от распределения этих термов по функциям. Однако исследования [9] показали, что число макроячеек PAL в разных схемах автоматов пропорционально отношению длин реализуемых ПСТ. При этом коэффициент пропорциональности зависит от числа q термов в макроячейках PAL, используемых для реализации схемы.

Окончательный выбор между известным подходом и предлагаемым методом можно сделать либо с использованием определенного программного обеспечения, либо аналитически.

Покажем, как это сделать аналитически для данного примера, если макроячейки PAL имеют q=3 терма. Пусть  $E_i(D_r)$ ,  $Q_i(D_r,q)$  соответственно число термов в функции  $D_r \in \Phi$  и число макроячек с q термами, требуемых для реализации функции в автомате Мура  $U_i(i=1,2)$ .

Для определения параметра  $Q_i(D_r,q)$  можно использовать результаты [5]

$$Q_i(D_r,q) = \left\lceil \frac{E_i(D_r) - q}{q - I} \right\rceil + I. \tag{17}$$

Построив полную ПСТ автомата  $S_I$  (модель  $U_2$ ) и проведя минимизацию функций  $D_r \in \Phi$  и использованием закона склеивания [1], получим:

$$E_2(D_1) = E_2(D_3) = 7$$

;  $E_2(D_2) = 10$ ;

$E_2(D_4) = 5$ .

Используя формулу (17), получим:

$$Q_2(D_1,3) = Q_2(D_3,3) = Q_2(D_4,3) = 3 ;$$

$$Q_2(D_2,3) = 5 .$$

Итак, для реализации схемы БФП в этом случае необходимо 14 макроячеек РАL. Анализ системы (13) показывает, что для реализации схемы БПК необходимо 4 макроячейки РАL, по две ячейки для каждой из функций  $\tau_r \in \tau$ .

Как уже отмечалось, для реализации системы микроопераций (14) достаточно 8 макроячеек РАL. Отметим, что эта величина не зависит от q, так как каждая микрооперация  $y_n \in Y$  представляется одним термом. Итак, для реализации логической схемы автомата  $S_I$  (модель  $U_2$ ) требуется 26 макроячеек РАL. Сделав подобный расчет для автомата Му-ра  $S_I$  (модель  $U_1$ ), получим 37 макроячеек РАL. Таким образом, применение модели  $U_2$  вместо  $U_1$  для автомата  $S_I$

позволяет уменьшить аппаратурные затраты в 1.42 раза. Кроме того, схема блока БВС для модели  $U_1$  имеет 3 уровня, а для модели  $U_2$  — только 2. Таким образом, в данном случае модель  $U_2$  обеспечивает и уменьшение времени такта цифровой системы.

#### Заключение

Предлагаемый метод обобщенного кодирования состояний автомата Мура позволяет уменьшить длину таблицы переходов до длины соответствующей таблицы эквивалентного автомата Мили. При этом число термов в системе выходных сигналов может быть уменьшено до числа микроопераций (N). Сжатие таблицы переходов достигается за счет ввода блока преобразователя кодов для некоторых классов псевдоэквивалентных состояний. Этот блок не вносит задержки в работу автомата, так как преобразование выполняется параллельно с выполнением микроопераций в исполнительной части цифровой системы. При выполнении условия (9), когда каждый класс представляется одним кодовым интервалом, блок БПК отсутствует. Использование БПК основано на особенностях макроячеек РАL [10]. Дополнительным эффектом предлагаемого метода является возможность уменьшения цикла автомата, благодаря уменьшению числа уровней в его логической схеме. Для исследования эффективности предложенного метода был реализован программный комплекс, использующий VHDL-модели автоматов  $U_1$  и  $U_2$  . Кодирование состояний и их классов выполнялось алгоритмом ESPRESSO [1]. Результирующие системы уравнений обрабатывались системой WebPack фирмы Xilinx [9], что позволило оценить число макроячеек РАL и быстродействие схем автоматов. Исследования показали, что обобщенное кодирование состояний позволяет получить схемы, потребляющие до 40% меньше макроячеек, чем для автоматов с произвольным кодированием состояний, и до 18% меньше, чем для автоматов с оптимальным кодированием состояний. При этом

число уровней в первом случае уменьшалось от 3 до 6, а во втором – от 1 до 3. Дальнейшее направление наших исследований связано с анализом применения предложенного метода при реализации устройств управления на FPGA и микросхемах CoolRunner [9].

### Литература

- 1. DeMicheli G. Synthesis and Optimization of Digital Circuits. McGraw-Hill, 1994. 636 p.

- 2. Baranov S. Logic Synthesis for Control Automata. Kluwer Academic Publishers, 1994. 312 p.

- 3. Грушницкий Р.И., Мурсаев А.Х., Угрюмов Е.П. Проектирование систем с использованием микросхем программируемой логики. СПб: БХВ-Петербург, 2002. 608 с.

- 4. Соловьев В.В. Проектирование цифровых схем на основе программируемых логических интегральных схем. М.: Горячая линия-ТЕЛЕКОМ, 2001. 636 с.

- 5. Kania D. Synteza logiczna przeznaczona dla matrycowych struktur programowalnych typu PAL. Zeszyty naukowe Politechniki Śląskiej, Gliwice, 2004. 240 p.

- 6. Баркалов А.А. Принципы оптимизации логической схемы микропрограммного автомата Мура // Ки-бернетика и системный анализ. 1998. № 1 С. 65-72.

- 7. Barkalov A., Wegrzyn M. Design of Control Units with Programmable Logic. Zielona Gora: University of Zielona Gora Press, 2006. 150 p.

- 8. FPGA, CPLID and Structured ASIC: Altera, the Leader in Programmable Logic [Электрон. ресурс]. Режим доступа: altera.com.

- 9. FPGA, CPLID Solutions from Xilinx, Inc. [Электрон. pecypc]. Режим доступа: xilinx.com.

- 10. Баркалов А.А., Цололо С.А. Оптимизация схемы автомата Мура в составе системы на кристалле // Радиоэлектроника и информатика. 2007. № 1. С. 35-39.

Поступила в редакцию 22.01.2008

**Рецензент**: д-р техн. наук, проф. Ю.А. Скобцов, Донецкий национальный технический университет, Донецк.